Research Article

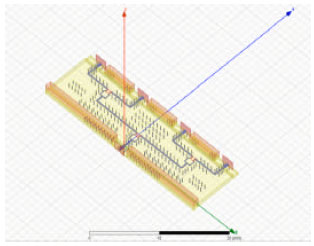

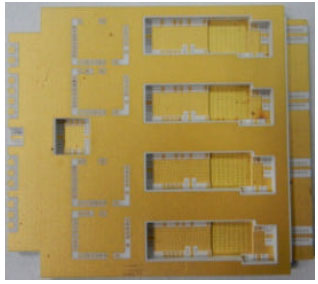

Design of a Highly Integrated Front-End K-Band TR Module Based on LTCC Technology for Phased-Array System

School of Aeronautics and Astronautics, Zhejiang University, 310027, Hangzhou, China

Hao Luo

School of Aeronautics and Astronautics, Zhejiang University, 310027, Hangzhou, China

Yong-Heng Shang

School of Aeronautics and Astronautics, Zhejiang University, 310027, Hangzhou, China

Fa-Xin Yu

School of Aeronautics and Astronautics, Zhejiang University, 310027, Hangzhou, China